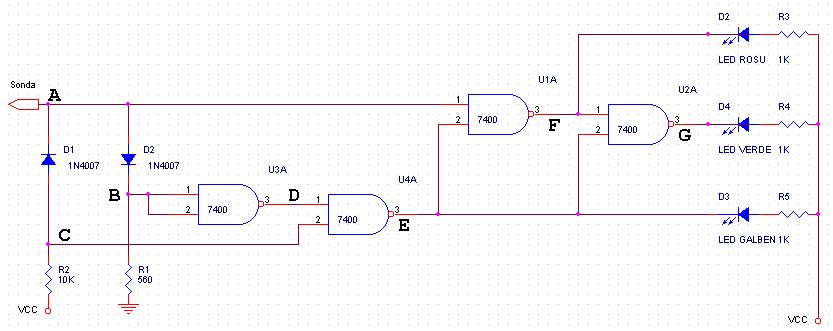

Montajul se alimenteazã la 5V c.c. Ledurile indicatoare ale valorilor

logice mãsurate sunt protejate de câte o rezistenãtã

de 1K. Ele lumineazã când E,F si G au valoarea 0

logic (E pentru z, F pentru 1 si G pentru 0

).

| D1 | D2 | A | B | C | D | E | F | G |

| OFF | ON | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| ON | OFF | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| OFF | OFF | z | 0 | 1 | 1 | 0 | 1 | 1 |

R1 conecteazã intrarea B la 0V cu posibilitatea ca intrarea sã

fie conectatã la +5V când pe intrarea A apare un nivel logic

HIGH.

R2 conecteazã intrarea C la +5V cu posibilitatea ca intrarea

sã fie conectatã la 0V când pe intrarea A apare un

nivel logic LOW.

- ea poate fi downloadatã (SondaXilinx.zip - 17KB) printr-un

click pe sageatã : ![]()

- imagini Test Xilinx :

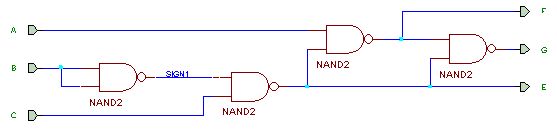

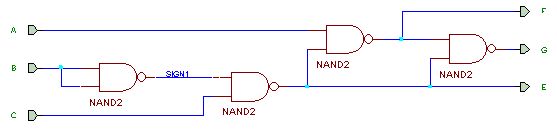

0) ![]()

1) ![]()

z) ![]()

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity sondab is

port(

A : in boolean;

B : in boolean;

C : in boolean;

F : inout boolean;

G : out boolean;

E : inout boolean

);

end sondab;

architecture sondab of sondab is

begin

process (A,E)

begin

F<=not(A and E);

end process;

process (B,C)

begin

E<=not((not B)and C);

end process;

process (F,E)

begin

G<=not(F and E );

end process;

end sondab;

Download sonda in VHDL : sondab.vhd : click aici : ![]()

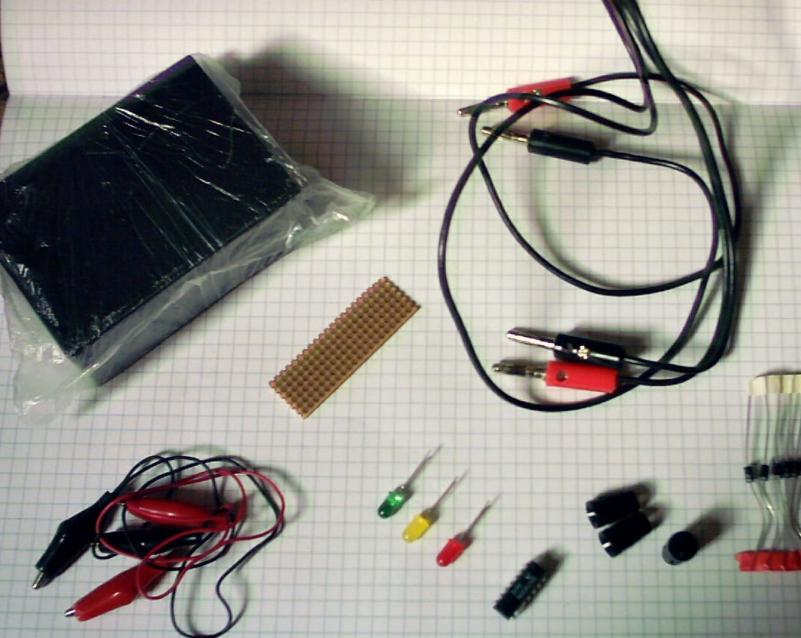

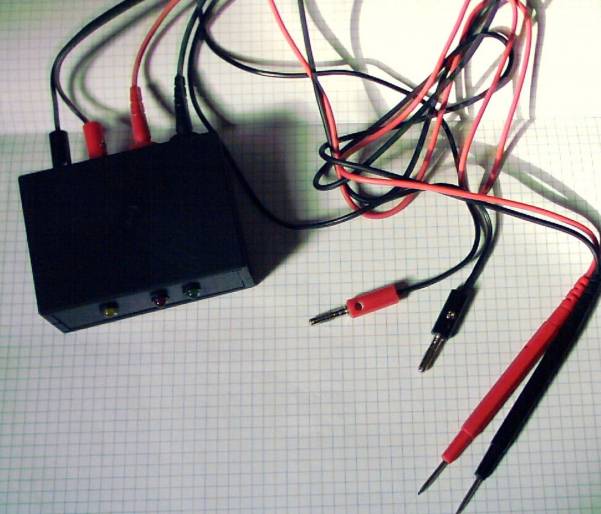

- partile componente ale sondei logice cu 3 leduri.

- partile componente ale sondei logice cu 3 leduri.

- vedere de sus.

- vedere de sus.

- vedere din fatza.

- vedere din fatza.

- vedere din spate.

- vedere din spate.